# TOPRO

# **TP6508**

# **Advanced Panel-2 Video Graphic Array**

# **Specification**

Version: 2.1 Revision: 2.02 1999/11/25

Topro Technology Incorporation

# **Revision History**

| <u>Revision</u> | Date .   | <u>Comment</u> .                                                                                    |

|-----------------|----------|-----------------------------------------------------------------------------------------------------|

| 2.02            | 88.04.12 | Change for Topro version.                                                                           |

| 2.1             | 88.10.13 | Update SREG CE bit-3 register description.                                                          |

|                 |          | Update 'Active' & 'Function' descriptions of FPVCC, FPVEE, FPBACK pins in Pin Descriptions chapter. |

|                 |          | Update "LCD Panel Power Sequencing" in Function Descriptions chapter .                              |

# **TP6508 Target Spec. List**

| Revision History                                 | 1   |

|--------------------------------------------------|-----|

| I. General Description                           | . 1 |

| II. Feature                                      | 3   |

| III. Pin Configurations                          |     |

| ISA Bus Interface Connections                    |     |

| PCI Local Bus Interface Connections              |     |

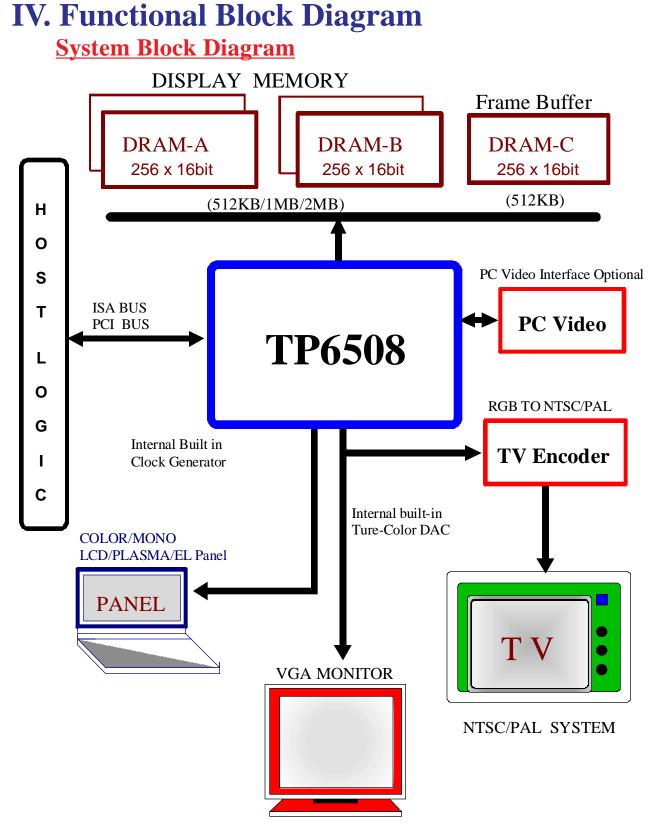

| IV. Functional Block Diagram                     |     |

| System Block Diagram                             |     |

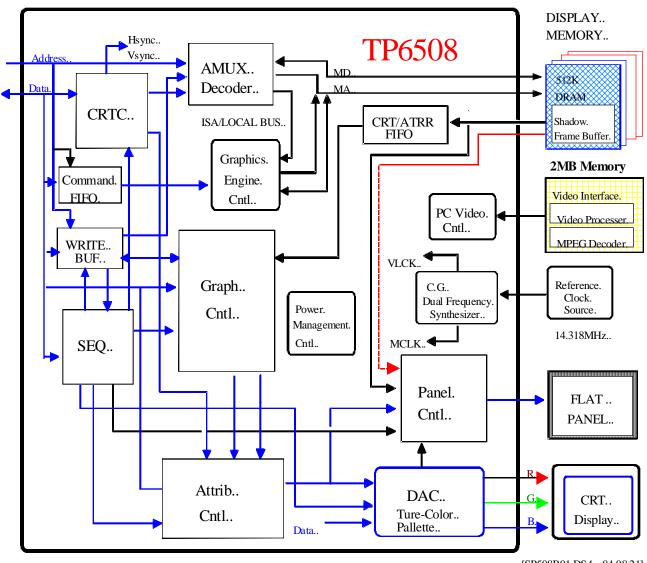

| VGA Block Diagram                                |     |

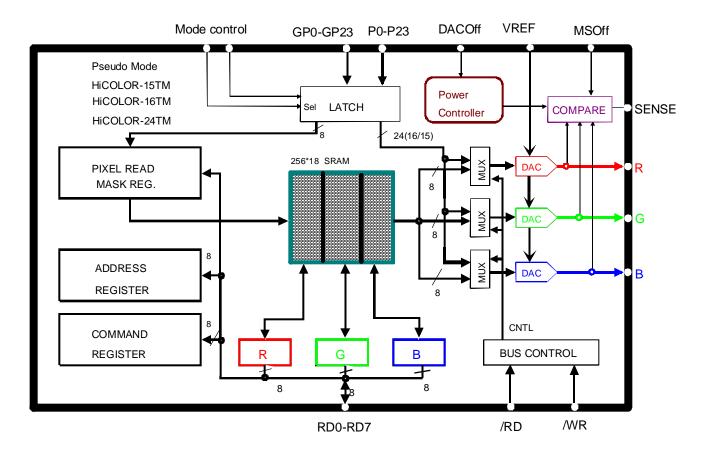

| True-Color Palette DAC Block Diagram             |     |

| Dual Frequency Synthesizer Block Diagram         |     |

| Panel Controller Block Diagram                   |     |

| Graphics Engine Diagram                          | 12  |

| Memory Configuration Block Diagram               | 13  |

| V. Pin Descriptions                              | 15  |

| VI. Function Descriptions                        |     |

| Host Bus Interface                               |     |

| Sequencer Controller (SEQC)                      |     |

| CRT Controller (CRTC)                            |     |

| Attribute Controller (ATC)                       |     |

| Graphics Controller (GFXC)                       | 27  |

| Address Multiplexer (AMUX)                       | 27  |

| CRT FIFO (Display FIFO)                          | 28  |

| Attribute FIFO                                   | 28  |

| Write Buffer                                     | 28  |

| Dual Frequency Synthesizer                       |     |

| True-Color Palette DAC (TDAC)                    |     |

| Graphics Engine Controller (GEC)                 |     |

| Command FIFO                                     |     |

| Hardware Cursor Controller                       |     |

| PC Video Controller                              |     |

| LCD Line Buffer                                  |     |

| Panel Controller                                 |     |

| Power Management Controller (P.M.C.)             |     |

| VII. Registers                                   |     |

| IBM Standard Register                            |     |

| Backward Compatible Register Description         |     |

| Extended Sequencer Register Description          |     |

| Extended CRTC Register Description               |     |

| Panel Control Register Description               |     |

| PCI Local Bus Configuration Register Description |     |

| Graphics Engine Control Register Description     | 85  |

| VIII. Absolute Maximum Rating                    |     |

|--------------------------------------------------|-----|

| IX. DC Electrical Characteristic                 |     |

| DC Characteristics                               |     |

| DAC Characteristics                              |     |

| DC Drive Characteristics                         |     |

| X. AC Electrical Characteristic                  |     |

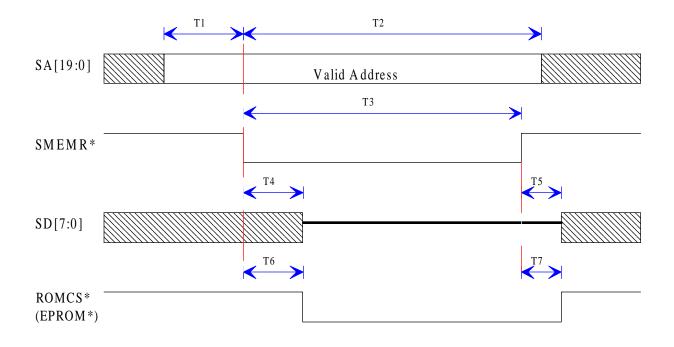

| BIOS ROM Interface Timing SPEC.                  |     |

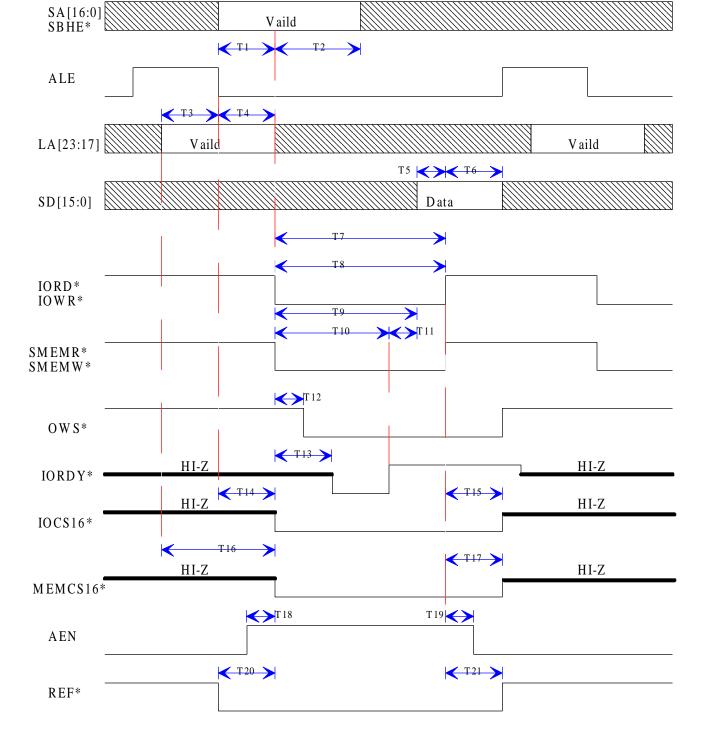

| ISA Bus Interface Timing SPEC.                   | 100 |

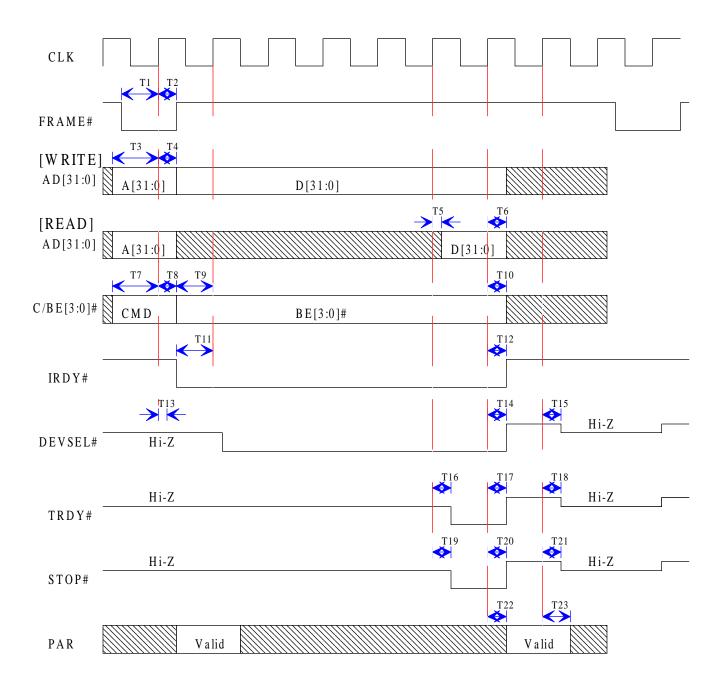

| PCI Local Bus Interface Timing SPEC.             | 101 |

| Memory Bus Interface Timing SPEC.                |     |

| Color-Key PC Video & VAFC Interface Timing       |     |

| RAMDAC & Feature Connector Interface Timing      |     |

| XI. Timing Diagrams                              |     |

| BIOS ROM Read Cycle                              |     |

| ISA Bus Interface Timing                         |     |

| PCI Local Bus Interface Timing (32-bit data bus) |     |

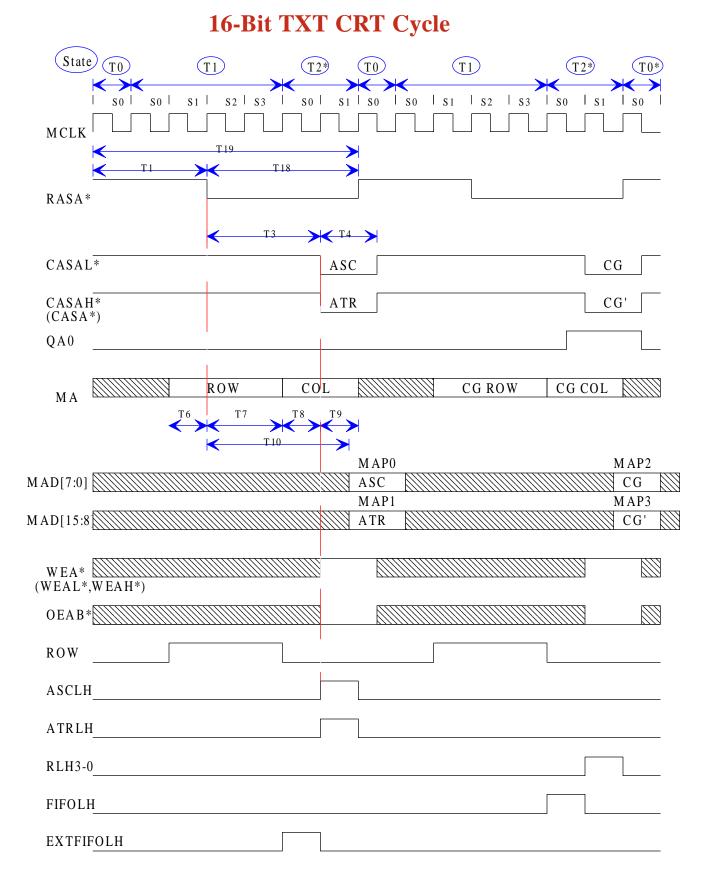

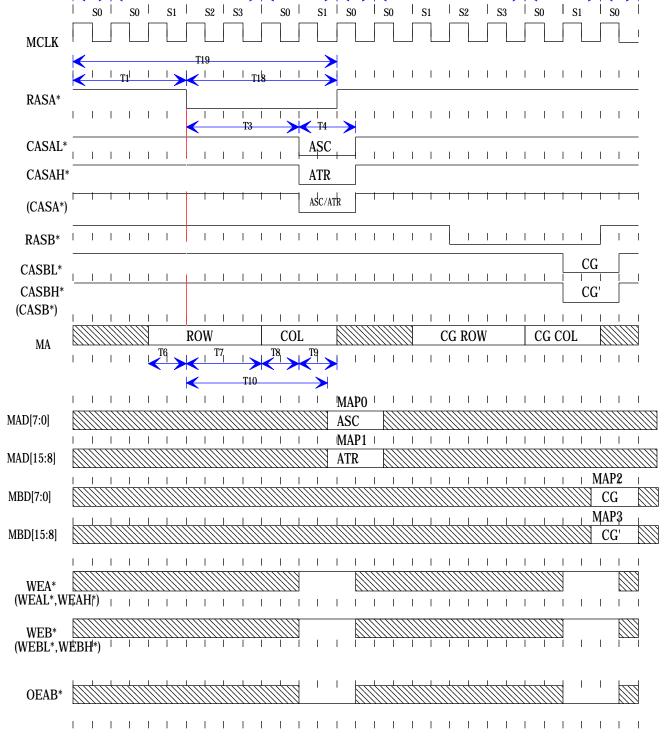

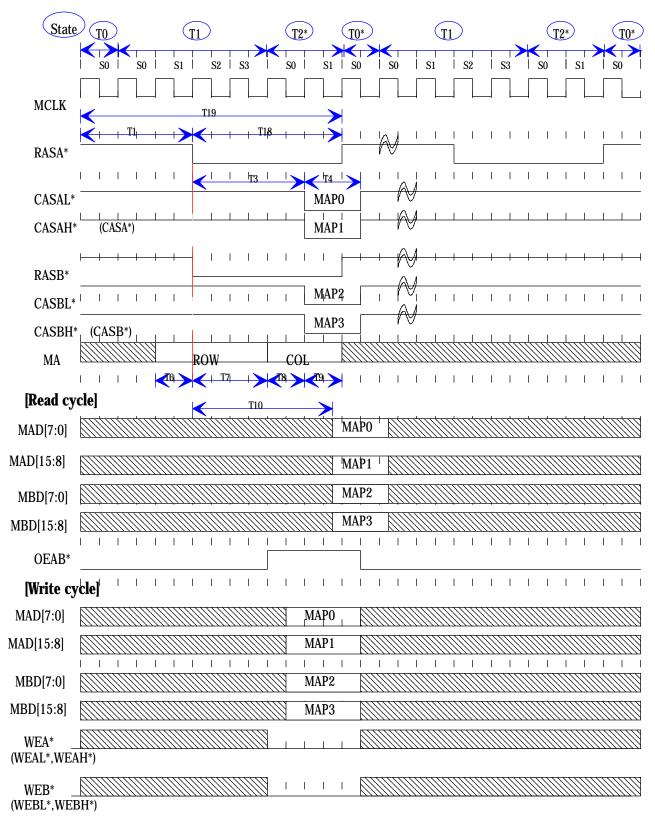

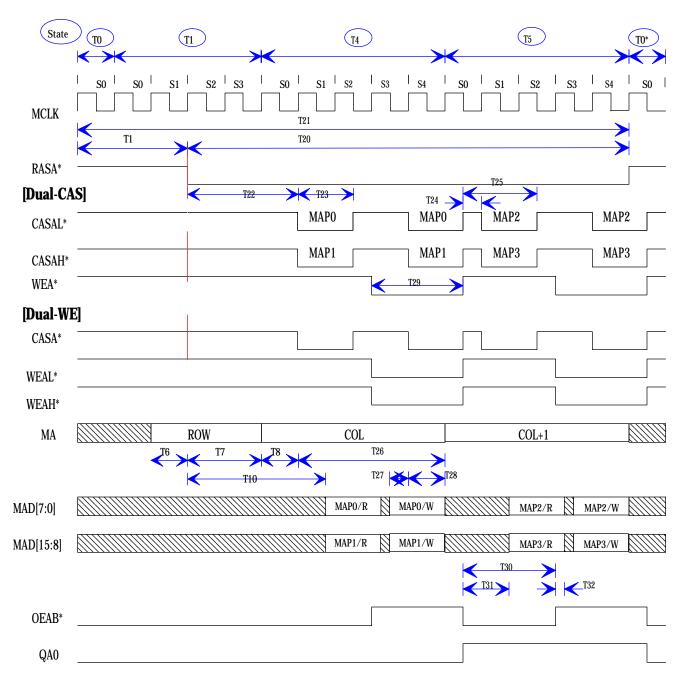

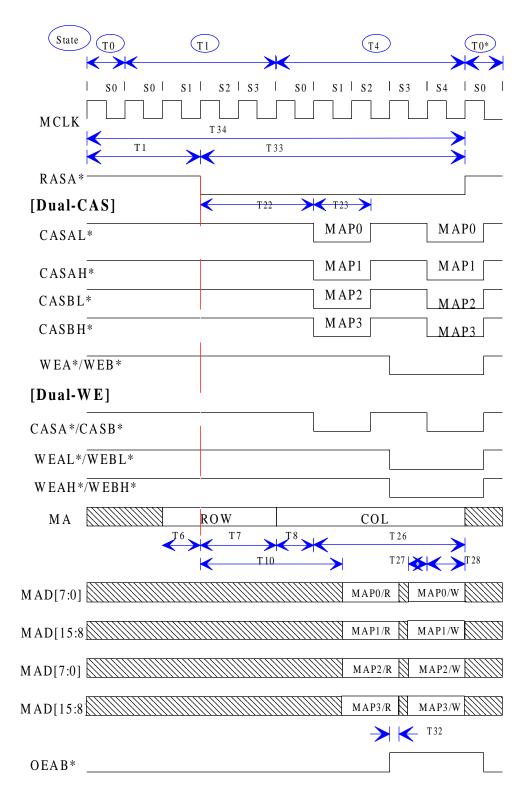

| 16-Bit TXT CRT Cycle                             |     |

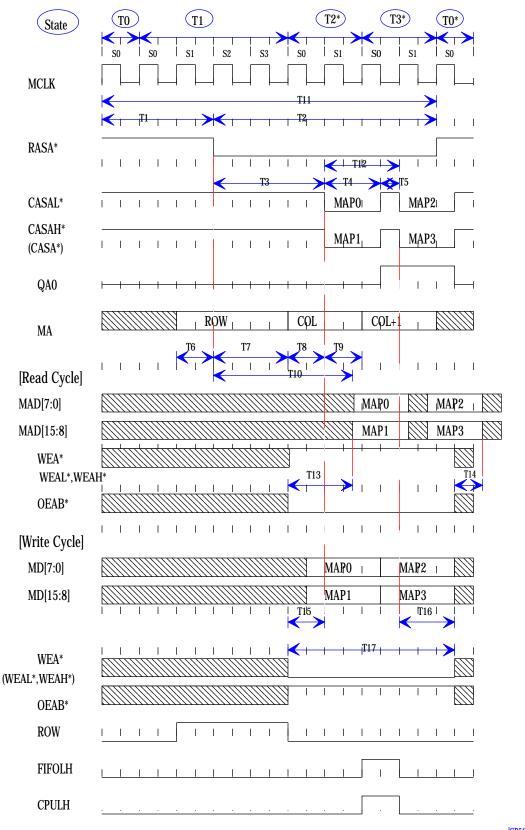

| 16-Bit CPU/GFX CRT/Shadow Frame Buffer Cycle     |     |

| 32-Bit TXT CRT Cycle                             |     |

| 32-Bit CPU/GFX CRT/Shadow Frame Buffer Cycle     |     |

| 16-Bit Read-Modify-Write Cycle                   |     |

| 32-Bit Read-Modify-Write Cycle                   |     |

| Refresh Cycle Cycle(CAS Before RAS)              |     |

| External Frame Buffer Interface Timing (16-bit)  |     |

| RAMDAC & Feature Connector Interface Timing      |     |

| Color-Key PC Video & VAFC Interface Timing       |     |

| XII. Appendix                                    |     |

| A. Monitor Specification                         |     |

| B. TP6508 VGA Modes                              |     |

| C. Rast Operation Code List                      |     |

| D. Memory Address Table                          |     |

| E. MCLK & VCLK Frequency Programming Table       |     |

| F. Pins Selection Configuration                  |     |

# **I. General Description**

The TP6508 is an advanced single-chip flat panel VGA controller . It's used for notebook or portable computer system with simple operation and powerful features. Also it contains all of the functions and supports logic required to implement the IBM VGA display standards and enhanced display modes on LCD, PLASMA,EL panel and TV display at register and BIOS level compatiable. A simultaneous display technology is implemented in TP6508 to be used for CRT/Flat panel, LCD/TV display.

For minimum chip-count or board-space, it is designed to complete a video subsystem with only one 256kx16 DRAM(512K Bytes). This video subsystem can support all panel type without any glue logic or external frame buffer.

Like general VGA graphics chips, the TP6508 includes CRT Controller (CRTC), Attribute Controller (ATRC), Graphic Controller (GFXC), Address Multiplexer (AMUX), Sequential Controller (SEQC) and adds a Graphics Engine Controller (GEC) to provide VGA display functions and to speed up the system operation. With the deeper CRT FIFO, and the multiple level CPU command FIFO (Write Buffer) / Read Cache, the TP6508 supports higher system performance even in minimum memory configurations.

In order to complete a video subsystem by two chips, VGA controller and DRAM, the TP6508 uses 208pin QFP to integrate Clock Generator(Dual frequency synthesizers), True-color RAMDAC, Display controller, Flat panel controller, Video-in interface, Graphics Engine Controller and Power management controller to minimizes the form factor requirement for VGA subsystem.

In addition to an ISA bus connection, it can be connected directly to PCI standard local bus interface to provide additional graphics performance without any glue logic.

TP6508 can support flat panel display, resolution up to 1024x768 mono, 800x600 hi-color, 640x480 true-color. Unlike on CRT, the pixels on a flat panel display are real, discrete entities of a fixed size. This results in problems when different display modes are mapped onto one panel. The TP6508 provides approach to keep the vertical resolution of the display mode constant but center the active display area vertically on the panel.

The flat panel interface supports Monochrome/Color STN LCD panel, Color TFT LCD panel, PLASMA panel and, EL panel. Providing direct panel interface to (DD) Dual-panel,Dual-drive for color and monochrome and (SS) Single-panel,Single-drive (supports 8,9,12,15,16,18,24-bit data). For Single-panel/Single-drive panel which refresh data rate is not high, the TP6508 can set some of the video memory as the frame buffer for panel display to decrease video memory chip counts to one (a 256kx16DRAM).

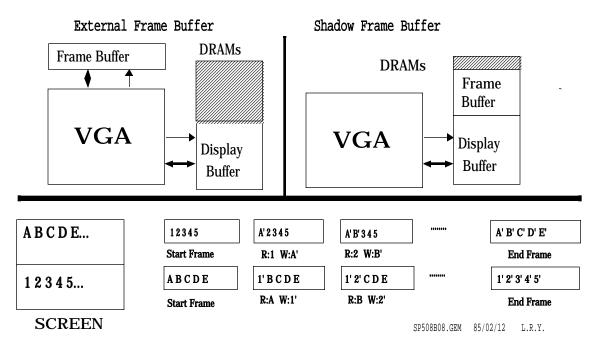

When the TP6508 is interfaced to a dual-scan mono STN LCD panel, an additional DRAM isn't needed with the shadow frame buffer technology. This shadow frame buffer build in video memory that is used by the chipset to accelerate panel refresh rate without using high frequency clocks, thus reducing power, and allowing vertical refresh rates from 60 Hz to 160 Hz for improved contrast and freedom from flicker.

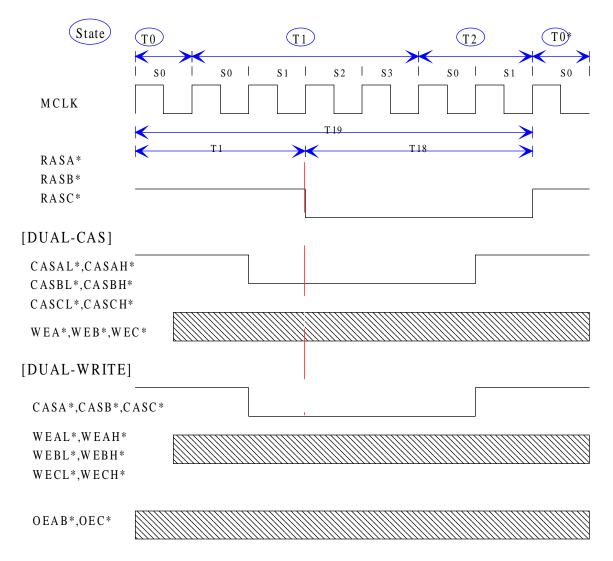

The TP6508 serves as a DRAM controller for the display memory, it handle DRAM refresh, display refresh, display memory access by CPU and supply the control signal of DRAM with dual-write or dual-cas.

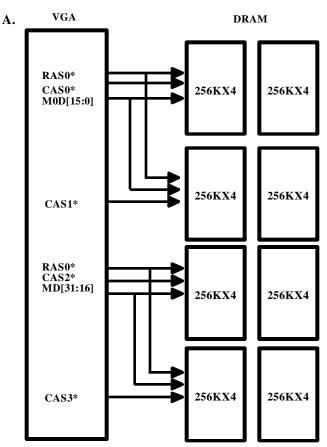

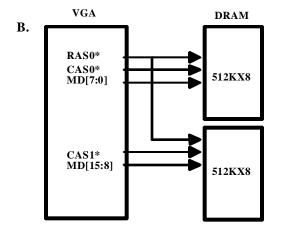

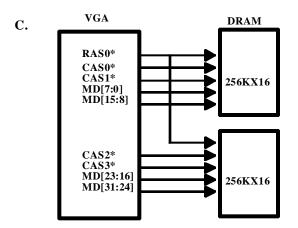

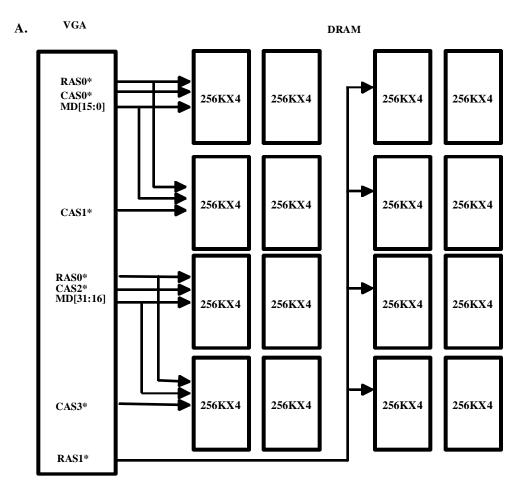

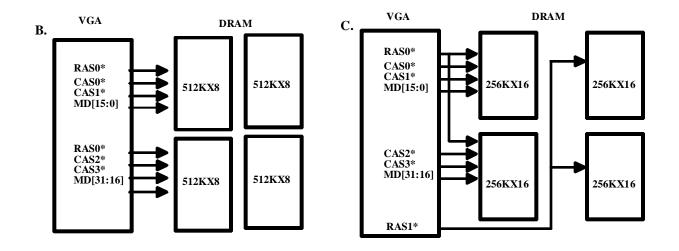

The TP6508 offers two types DRAM to make various memory configurations including of 512k , 1024k , 2048k memory size for different market. TP6508 support 256k x 4-bit , or 256k x 16-bit DRAM memory to simplify VGA system and implement high resolution display simultaneously. With Random Memory Cycle allocation skill and the multiple level CPU write buffer, the TP6508 provide better system performance and achieve zero wait state during memory write accesses.

When using DRAM 256kx16 by 1 or DRAM 256kx4 by 4, memory size is 512k byte and data width is 16 bits. When using 256kx16 by 2 or 256kx4 by 8, memory size is 1M byte and data size is 32 bits. TP6508 can support the CRT display resolution up to 1024x768 256 color non-interlace, 800x600 hi-color,640x480 true color at 1M byte display memory. When using 256kx16 by 4, memory size is 2M byte and data size is 32 bits. All display-memory can be linear addressing.

The Video-in interface accept video signal from PC-video.

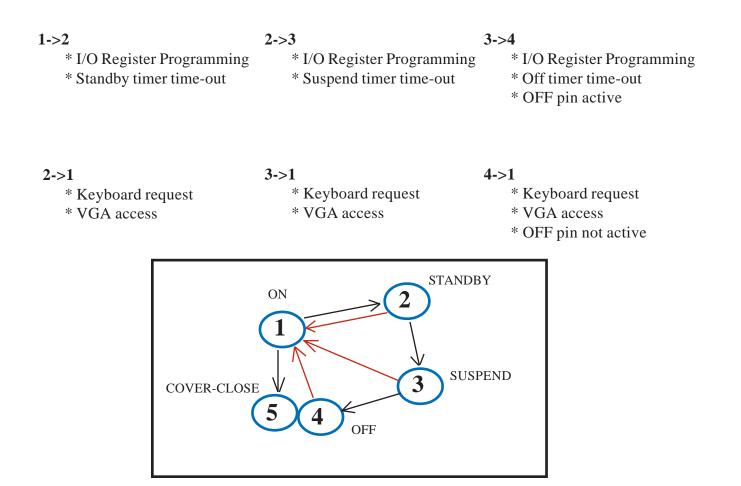

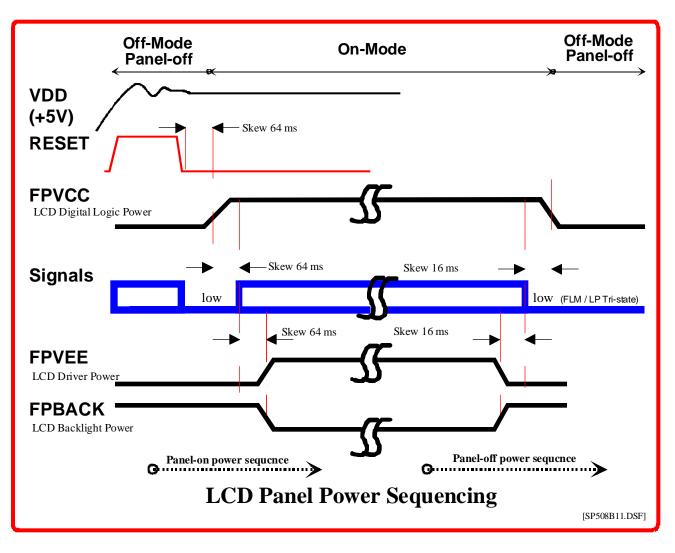

Providing the power sequential control for flat panel . FPVCC signal is applied to the digital +5V voltage of flat panel, FPVEE signal is applied to the analog Driver's bias voltage of flat panel, and FPBACK signal is applied to the Invertor for the backlight of flat panel, their on/off sequence is programmable. Anotherway TP6508 providing intelligent control by timer to switch power mode (On including Cover-close,standby,suspend,Off) to save the power of TP6508 and Display.

The TP6508 graphics chip has been designed to optimize cost/performance trade-off considerations. The Video clock rate depends upon the mode used, and is up to 135 MHz. The Memory clock input is optional and depends on the display DRAMs access-time . It can be up to 75 MHz.

# **II. Feature**

. 208-pin single chip design

- . IBM VGA hardware compatible

- . Integrates RAMDAC

- Support 24-bit True-color resolution

- Up to 135 MHz pixel rate

- Low power control

- Implement Monitor-Sense feature

- . Integrates Clock Generator

- Programmable dual frequency synthesizer

- Up to 135 MHz clock rate for VCLK synthesier

- Up to 75 MHz clock rate for MCLK synthesier

- External Power-down mode Clock Source optional

### . Memory DRAM configuration support

- Support symmetric or asymmetric RAS/CAS address DRAM

- Support dual-CAS or dual-WE addressing DRAM

- 512k Bytes Memory:four 256kx4-bit /one 256kx16-bit

- 1M Bytes Memory:eigh 256kx4-bit /two 256kx16-bit

- 2M Bytes Memory:sixteen 256kx4-bit/four 256kx16-bit

### . Bus support

- ISA Bus with Zero-wait state assertion

- 32-bit data width PCI Local Bus

### . Provide linear addressing

- Relocation VGA memory address at over 1M-byte address location

### . Integrates STN panel support

- Support Dual/single scan mono STN LCD Panel,

- up to 64 simultaneous grays

- Support Dual/single scan color STN LCD Panel

- up to 64k simultaneous colors, and 61<sup>3</sup> visual color

- Provide 8 and 16 bit panel interfaces

### . Integrates color TFT panel support

- Support Normal or CRT-like TFT LCD panel

- Support 9/12/15 or 18/24 bit panel interface, and up to 16.8M simultaneous colors

### . Support panel resolution up to 800x600 for STN and TFT LCD flat panel

### . Simultaneous Display operation

- Simultaneous LCD and CRT display

- Simultaneous PLASMA and CRT display

- Simultaneous EL and CRT display

- Simultaneous LCD and TV display

### . VGA BIOS decoding

- Provide 64k-byte or 32k-byte VGA BIOS decoding

### . Dual-scan STN Frame Buffer

- Shadow Frame Buffer onto display memory for mono or color LCD panel

- Pseudo Frame Buffer for color LCD panel (no additional DRAMs required)

- External Frame Buffer for color LCD panel (external additional DRAMs required)

### . Provide PC Video interface

- Provide VESA Advanced Feature Connector(VAFC) interface

- Provide color-key PC video interface

### . High Performance architecture

- Provide 4 stages CPU Write Buffer

- Provide 8 stages Command FIFO for graphics engine access

- Offer 20 stages CRT FIFO and 8 stages Attribute FIFO

### . Integrates hardware cursor function

- 64 by 64 pixels (2-bit)

- Offer Color 0,1, inversion and transparency operation

### . Windows performance-improvement feature

- Bit block transfer (8/16/24 bit color mode) including of Image read/write

- Color expansion (8/16/24 bit mode)

- Line drawing (8/16/24 bit mode)

- Rectangular clipping (8/16/24 bit mode)

- Rectangular fill and Pattern fill(8/16/24 bit mode)

### . Graphics Engine I/O command addressing

- Programmable I/O base command

- Memory mapping I/O command

### . Intelligent Power Management

- Built-In Power Management controller

- Multiple level power down modes (On/Standby/Suspend/Off mode)

- Automatic activity monitoring

- Flexible mode transition Control (Pin control/Timer out/Register programming /VGA access and Keyboard request trigger return)

- Automatic flat panel power sequencing

- Programmable slow refresh rate

### . Enhanced mode includes:

- 132x25 or 132x44 text mode

- 640x480/256 colors (Windows acceleration mode support optional)

- 640x480/65536 colors (Windows acceleration mode support optional)

- 640x480/16.8M colors (Windows acceleration mode support optional)

- 800x600/16 colors

- 800x600/256 colors (Windows acceleration mode support optional)

- 800x600/65536 colors (Windows acceleration mode support optional)

- 800x600/16.8M colors

- 1024x768/16 colors

- 1024x768/256 colors (Windows acceleration mode support optional)

1024x768/65536 colors (Windows acceleration mode support optional)

- 1280x1024/16 colors

- 1280x1024/256 colors (Windows acceleration mode support optional)

1600x1280/16 colors interlace display mode

57

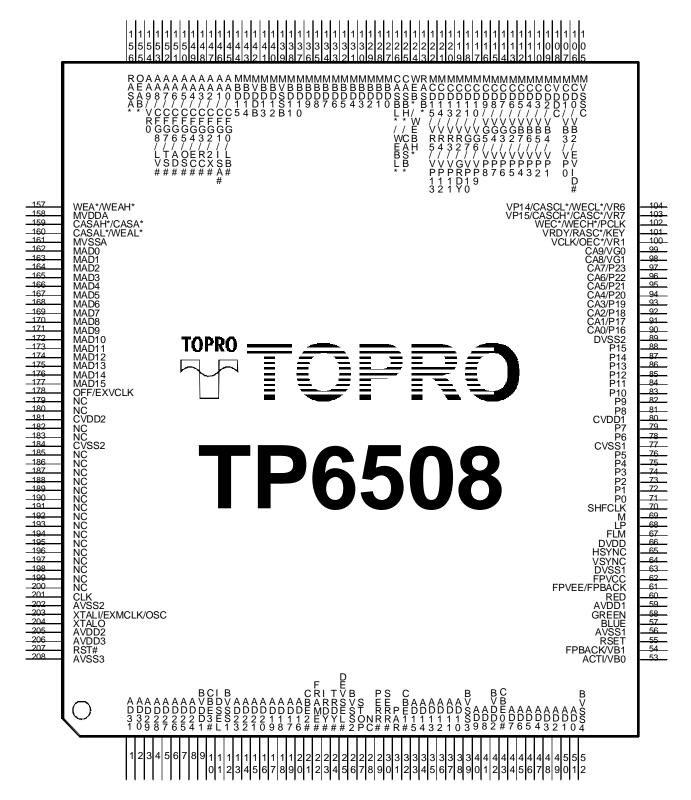

# **III. Pin Configurations**

20.3

LA18 LA19

LA20 LA21 LA22

ATALI/E XTALO AVDD2 AVDD3 RESET AVSS3

AVSS2 XTALI/EXMCLK/OSC

## **ISA Bus Interface Connections**

FPVCC FPVEE/FPBACK AVDD1 GREEN

BLUE

AVSS1 RSET FPBACK/VB1 ACTI/VB0

# **PCI Local Bus Interface Connections**

$1280 \ X \ 1024 \ / \ 256$  ,  $800 \ X600 \ / \ 16.8 M$  COLORS FLAT PANEL/CRT DISPLAY SYSTEM

[SP508B05.DS4 86/04/15 L.R.Y.]

# VGA Block Diagram

[SP508B01.DS4 84.08.21]

# **True-Color Palette DAC Block Diagram**

[SP508B02.DS4 85/03/11 L.R.Y.]

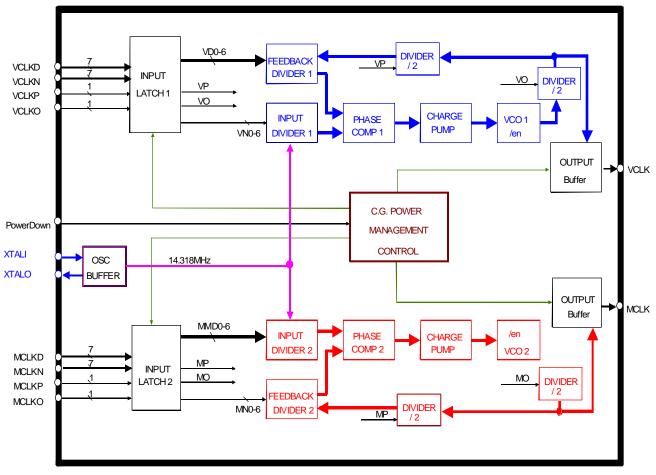

# **Dual Frequency Synthesizer Block Diagram**

[SP508B03.DS4 85/03/11 L.R.Y.]

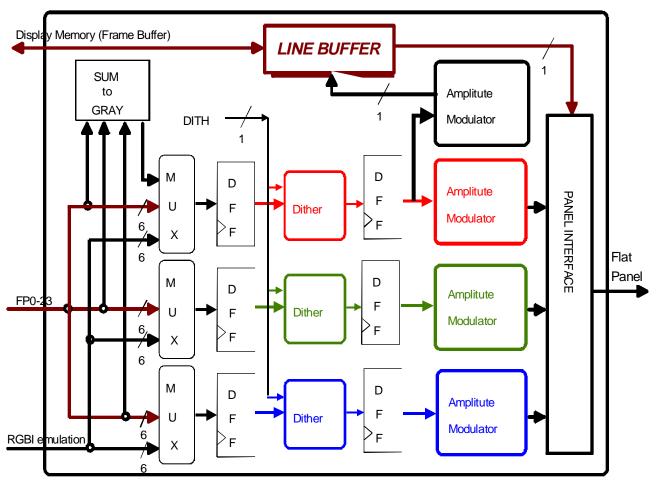

# **Panel Controller Block Diagram**

<sup>[</sup>SP508B04.DS4 85/03/11 L.R.Y.]

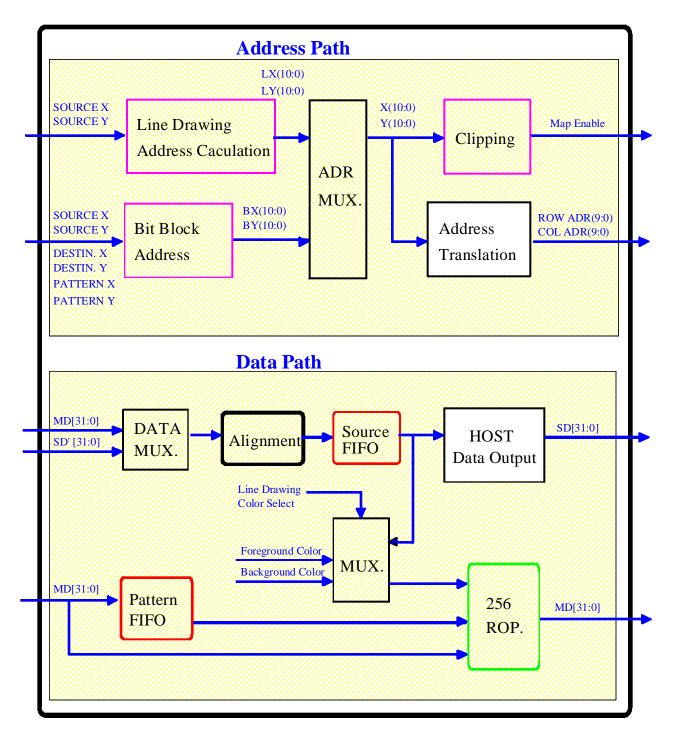

# **Graphics Engine Diagram**

[SP508B12.DS4 85.08.21]

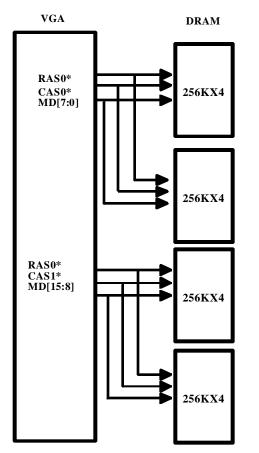

# **Memory Configuration Block Diagram**

### 512 K MEMORY DRAM(S) CONFIGURATION

[SP508B06.DS4 84/05/23]

# 1024K MEMORY DRAM(S) CONFIGURATION

### 2048K MEMORY DRAM(S) CONFIGURATION

[SP508B06.DS4 84/05/23]

# **V. Pin Descriptions**

# \* ISA Bus Interface (54 pins)

| Symble                               | Туре                         | Drive | Pin Number                                                                    | Active | Function                                                                                                                                                 |

|--------------------------------------|------------------------------|-------|-------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD[15:0]                             | I/O                          | 8maR  | 33,34,35,36,37<br>38,40,41,44,45<br>46,47,48,49,50,51                         | True   | These signals provide 16 data bits transfer on ISA bus with system microprocessor.                                                                       |

| SA[16:2]<br>SA[1:0]                  | I (I/O)<br>I                 | -     | 195,194,193,192,191,<br>190,189,188,187,186,<br>185,183,182,180,179,<br>21,43 | True   | Address Bit 16 Through 0 are used to address frame buffer and I/O ports with TP6508.                                                                     |

| LA[23:22]<br>A21<br>A20<br>LA[19:17] | I<br>I (I/O)<br>I<br>I (I/O) | -     | 28,201,200,199,198,<br>197,196                                                | True   | Address Bit 23 Through 17 are used to<br>address frame buffer and I/O ports with TP6508.<br>In general ,these signals are not gated address<br>LA[19:17] |

| AEN                                  | I<br>(I/O)                   | -     | 31                                                                            | High   | A high active signal used to detect the TP6508 from the I/O channel to avoid a disturbance from the DMA controller.                                      |

| ALE                                  | Ι                            | -     | 22                                                                            | High   | This signal is used to latch those ungated ad-<br>dress bus.                                                                                             |

| SBHE*                                | Ι                            | -     | 32                                                                            | Low    | It indicates and enables transfer of data on the<br>high byte of data bus and is used with A0 to dis-<br>tinguish between high and low byte.             |

| IORD*                                | I<br>(I/O)                   | -     | 27                                                                            | Low    | I/O read signal comes from a host micropro-<br>cessor to read data from TP6508 control.                                                                  |

| IOWR*                                | I<br>(I/O)                   | -     | 25                                                                            | Low    | I/O write signal comes from a host micropro-<br>cessor to read data from TP6508 control regis-<br>ters.                                                  |

| MEMR*                                | Ι                            | -     | 11                                                                            | Low    | Memory read signal comes from a host<br>microprocessor to read data from video<br>memory.                                                                |

| MEMW*                                | Ι                            | -     | 23                                                                            | Low    | Memory write signal comes from a host<br>microprocessor to read data from video<br>memory.                                                               |

| IORDY*                               | ОТ                           | 12maR | 24                                                                            | Low    | This signal is driven low by TP6508 to lengthen<br>the memory or I/O accessed cycle.                                                                     |

| IOCS16*                              | OT<br>(I/O)                  | 12maR | 18                                                                            | Low    | This signal is driven low to indicate that the TP6508 can execute an I/O operation at the address currently on the 16-bit bus mode.                      |

| MEMCS16*                             | OT<br>(I/O)                  | 12maR | 19                                                                            | Low    | This signal drives a 16-bit memory cycle for 16-bit bus data transfer.                                                                                   |

| RESET*                               | I/S                          | -     | 207                                                                           | Low    | This pin is connected to the signal that was in-<br>verted from the system board to reset the<br>TP6508.                                                 |

| IRQ                                  | OT<br>(I/O)                  | 8maR  | 30                                                                            | Low    | The vertical retrace interrupt.                                                                                                                          |

| REF*                                 | I                            | -     | 10                                                                            | Low    | This signal is driven by system mother board<br>logic and is used to indicate a memory<br>refresh cycle is in operation.                                 |

| OWS*                                 | OT<br>(I/O)                  | 8maR  | 20                                                                            | Low    | This signal is driven by TP6508 to short the memory accessed cycle for improving system performance.                                                     |

# \* PCI Local Bus Interface (48 pins)

| Symble     | Туре         | Drive | Pin Number                                                                                                | Active | Function                                                                                                                                                                                                              |

|------------|--------------|-------|-----------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD[31:0]   | I/O          | 8maR  | 1,2,3,4,5,<br>6,7,8,13,14,<br>15,16,17,18,19,20,<br>33,34,35,36,37<br>38,40,41,44,45<br>46,47,48,49,50,51 | True   | Address and Data are multiplexed on the same<br>PCI Bus interface. A Bus transaction consists<br>of an address phase followed by one or more<br>data phase.                                                           |

| C/BE[3:0]# | Ι            | -     | 10,21,32,43                                                                                               | True   | Bus Command and Byte Enable are multiplexed<br>on the same PCI Bus interface. During the ad-<br>dress phase of a transaction, they define the Bus<br>Command. During the data phase, they are used<br>as Byte Enable. |

| PAR        | OT<br>(I/O)  | 4maR  | 31                                                                                                        | True   | Parity is even part across AD[31:0] and C/BE[3:0]#. Parity generation is required by all PCI agents.                                                                                                                  |

| FRAME#     | Ι            | -     | 22                                                                                                        | Low    | This input signal is used to indicate the beginning and duration of an access.                                                                                                                                        |

| TRDY#      | ОТ           | 12maR | 24                                                                                                        | Low    | This signal is driven to indicate TP6508's abil-<br>ity to complete the current data phase. It is used<br>in conjunction with IRDY#.                                                                                  |

| IRDY#      | Ι            | -     | 23                                                                                                        | Low    | This input signal is to indicate Bus master's abil-<br>ity to complete the current data phase. It is used<br>in conjunction with TRDY#.                                                                               |

| IDSEL      | Ι            | -     | 11                                                                                                        | High   | This signal is used as a chip select during con-<br>figuration read and write access.                                                                                                                                 |

| RESET#     | I/S          | -     | 207                                                                                                       | Low    | This signal is used to reset the TP6508 video device into initial state.                                                                                                                                              |

| CLK        | Ι            | -     | 201                                                                                                       | True   | This is the timing reference for TP6508 when connected to PCI Local Bus.                                                                                                                                              |

| DEVSEL#    | OT<br>(I/O)  | 12maR | 25                                                                                                        | Low    | This signal is driven to indicate that TP6508 video device has been selected . So TP6508 has decoded its address as the target of the current access.                                                                 |

| STOP#      | OT<br>(I/O)  | 4maR  | 27                                                                                                        | Low    | This signal is output to indicate that TP6508 is requesting the master to stop the current transaction.                                                                                                               |

| PERR#      | O/T<br>(I/O) | 8maR  | 29                                                                                                        | Low    | This signal is used for the reporting of data par-<br>ity erros. PERR# will be driven high for one<br>clock before being tristated as with all sustained<br>tristate signals.                                         |

| SERR#      | O/T<br>(I/O) | 8maR  | 30                                                                                                        | Low    | This signal is used for the reporting of system erros.                                                                                                                                                                |

### \* Display Memory Interface (82 pins)

|                    | •            |              |                                                                             |        |                                                                                                                                                                                                                                                    |

|--------------------|--------------|--------------|-----------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symble             | Туре         | Drive        | Pin Number                                                                  | Active | Function                                                                                                                                                                                                                                           |

| AA9<br>AA[8:0]     | I/O<br>I/O/U | 4maR<br>4maR | 154,153,152,151,150,<br>149,148,147,146,145                                 | True   | Display memory address bit 9 to 0 for DRAMs A and B. A pull-high mechanism gives a default high value in those configuration data.                                                                                                                 |

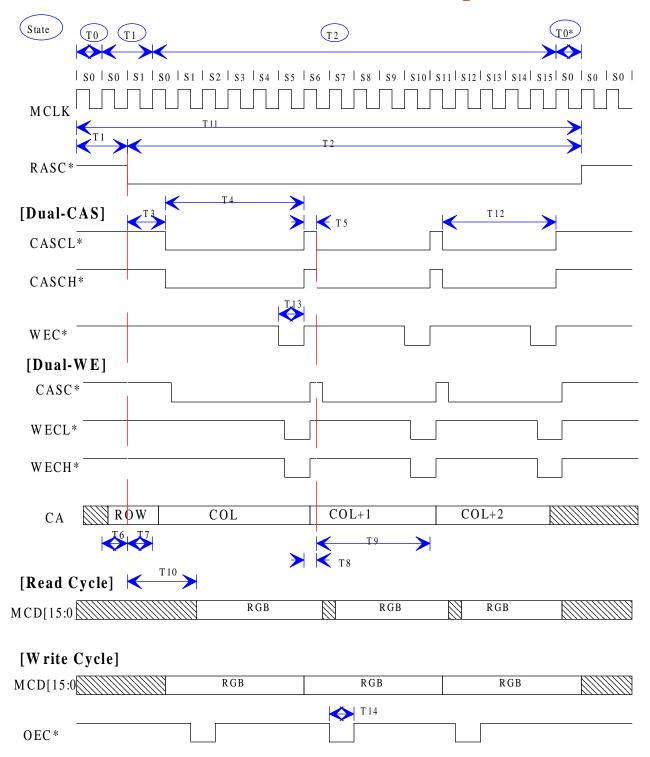

| CA[9:8]<br>CA[7:0] | I/O<br>O     | 4maR<br>4maR | 99,98,97,96,95,<br>94,93,92,91,90                                           | True   | Display memory address bit 9 to 0 for DRAMs C.                                                                                                                                                                                                     |

| MAD[15:0]          | I/O/U        | 4maR         | 177,176,175,174,173,<br>172,171,170,169,168,<br>167,166,165,164,163<br>162  | True   | These pins are used to transfer data between the TP6508 and display memory, DRAM A. A pull-high mechanism gives a default high value in those configuration data.                                                                                  |

| MBD[15:0]          | I/O          | 4maR         | 144,143,141,140,138,<br>137,136,135,134,133,<br>132,131,130,129,128,<br>127 | True   | These pins are used to transfer data between the TP6508 and display memory, DRAM B.                                                                                                                                                                |

| MCD[15:0]          | I/O          | 4maR         | 122,121,120,119,118,<br>117,116,115,114,113,<br>112,111,110,109,107,<br>106 | True   | These pins are used to transfer data between the TP6508 and frame buffer memory, DRAM C. When a frame buffer DRAM isn't requireed, this bus may optionall be used to input up to 24 bits of RGB data from the external PC-Video subsystem(device). |

| RASA*              | 0            | 4maR         | 156                                                                         | Low    | Row address strobe for latching 10-bit row ad-<br>dress signal into display memory, DRAM A                                                                                                                                                         |

| RASB*              | 0            | 4maR         | 123                                                                         | Low    | Row address strobe for latching 10-bit row ad-<br>dress signal into display memory, DRAM B                                                                                                                                                         |

| RASC*              | I/O          | 4maR         | 101                                                                         | Low    | Row address strobe for latching 10-bit row ad-<br>dress signal into display memory, DRAM C                                                                                                                                                         |

| CASAL*/WEAL*       | 0            | 4maR         | 160                                                                         | Low    | Column address strobe for DRAM A lower byte<br>in dual-CAS application. In dual-WE applica-<br>tion, it is used as write enable signal for DRAM<br>A lower byte.                                                                                   |

| CASAH*/CASA*       | 0            | 4maR         | 159                                                                         | Low    | Column address strobe for DRAM A upper bytein dual-CAS application.                                                                                                                                                                                |

| CASBL*/WEBL*       | 0            | 4maR         | 126                                                                         | Low    | Column address strobe for DRAM B lower bytein dual-CAS application.                                                                                                                                                                                |

| CASBH*/CASB*       | 0            | 4maR         | 125                                                                         | Low    | Column address strobe for DRAM B upper<br>byte.in dual-CAS application.                                                                                                                                                                            |

| CASCL*/WEAL*I/O    | 4maR         |              | 104                                                                         | Low    | Column address strobe for DRAM C lower<br>bytein dual-CAS application.                                                                                                                                                                             |

| CASCH*/CASC*       | I/O          | 4maR         | 103                                                                         | Low    | Column address strobe for DRAM C upper<br>bytein dual-CAS application.                                                                                                                                                                             |

| WEA*/WEAH*         | 0            | 4maR         | 157                                                                         | Low    | Write enable signal for DRAM A in dual-CAS application. In dual-WE application, it is used as write enable signal for DRAM A upper byte.                                                                                                           |

| WEB*/WEBH*         | 0            | 4maR         | 124                                                                         | Low    | Write enable signal for DRAM Bin dual-CAS application.                                                                                                                                                                                             |

| WEC*/WECH*         | 0            | 4maR         | 102                                                                         | Low    | Write enable signal for DRAM Cin dual-CAS application.                                                                                                                                                                                             |

| OEAB*              | 0            | 8maR         | 155                                                                         | Low    | Data output enable signal for DRAM A and DRAM B.                                                                                                                                                                                                   |

| OEC*               | I/O          | 4maR         | 100                                                                         | Low    | Data output enable signal for DRAM C.                                                                                                                                                                                                              |

### \* CRT Output interface (6 pins)

| Symble                 | Туре                                            | Drive                | Pin Number     | Active               | Function                                                                                                                                                                                                                                            |

|------------------------|-------------------------------------------------|----------------------|----------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

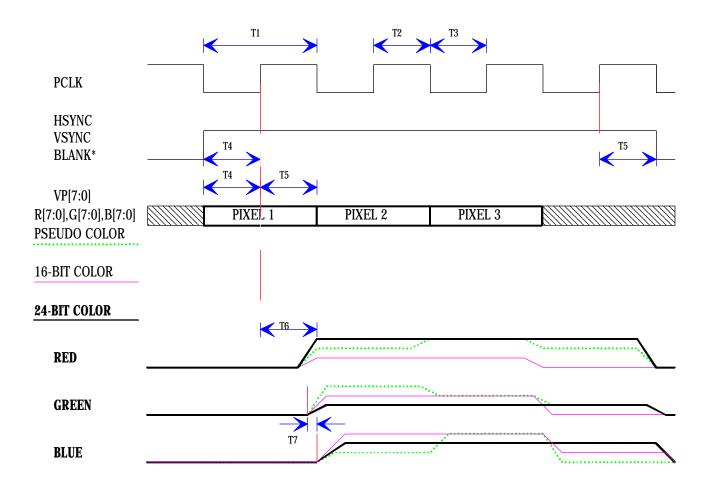

| RED<br>GREEN<br>BLUE   | Analog Output<br>Analog Output<br>Analog Output | 20ma<br>20ma<br>20ma | 60<br>58<br>57 | -                    | These three analog outputs are generated by TP6508's internal build-in DAC and it supplies current corresponding to the red , green , blue                                                                                                          |

| RSET                   | Analog Output                                   | 10ma                 | 55             | -                    | value of pixel being displayed.<br>This pin input is used as the internal build-in<br>RAMDAC voltage reference. A setting resister<br>is required between this pin and AVSS1 deter-<br>mines the full-scale output of each DAC.                     |

| VSYNC                  | 0                                               | 12maR                | 64             | True                 | Vertical retrace synchronization signal drives<br>the CRT monitor.                                                                                                                                                                                  |

| HSYNC                  | Ο                                               | 12maR                | 65             | True                 | Horizontal retrace synchronization signal drives<br>the CRT monitor.                                                                                                                                                                                |

| * Clock In             | put Interfac                                    | ce (4 pi             | ns)            |                      |                                                                                                                                                                                                                                                     |

| XTALI<br>EXMCLK<br>OSC | I<br>I<br>I                                     | -                    | 203            | True<br>True<br>True | The pin serves as the crystal input.<br>External memory clock input.<br>It requires an input frequency of 14.318MHz<br>with a duty cycle of 50+/-5%. This input pin sup-<br>plies the reference frequency for the Dual-fre-<br>quency Synthesizer . |

| XTALO                  | 0                                               | _                    | 204            | True                 | The pin serves as the crystal output .                                                                                                                                                                                                              |

| EXVCLK                 | I<br>(I/O)                                      | -                    | 178            | True                 | External video clock input It is a optional input from STANBY pin.                                                                                                                                                                                  |

| 32KHZ                  | I<br>(I/O)                                      | -                    | 154            | True                 | Refresh clock input for DRAMs under into OFF mode (VESA DPMS).                                                                                                                                                                                      |

| * MISC. I              | Pins (2 pins)                                   |                      |                |                      |                                                                                                                                                                                                                                                     |

| ROMCS*                 | 0<br>(I/O)                                      | 8maR                 | 29             | Low                  | VGA BIOS ROM enable signal for ISA bus, it generated by HM86509 when the 32k-byte                                                                                                                                                                   |

| TEST | I/O | 4maR | 178 | True |

|------|-----|------|-----|------|

memory location from C0000 to C7fff or the 64k-byte memory domain setting by extended

This pin is intended for testing. It can be rede-

fined as other useful function pin at the combination switch type of description in extended reg-

registers is selected.

ister Hex CC .

### \* Flat Panel Interface (28 pins)

| Symble                  | Туре       | Drive        | Pin Number                                                                             | Active               | Function                                                                                                                                                                                                            |

|-------------------------|------------|--------------|----------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SHFCLK(CL2)             | 0          | 12maR        | 70                                                                                     | True                 | This signal is used to driver the flat panel shift clock .                                                                                                                                                          |

| LP(CL1)<br>PHSYNC<br>DE | ОТ         | 8maR         | 68                                                                                     | High<br>True<br>High | This signal is used to drive the flat panel line<br>clock for LCD panels or the horizontal sync for<br>PLASMA/EL panels and some TFT panels. It<br>can also do as the display enable signal (DE)<br>for flat panel. |

| FLM<br>PVSYNC           | ОТ         | 8maR         | 67                                                                                     | High<br>True         | This signal is used to start a new frame on flat<br>panels for LCD panels or the vertical sync for<br>PLASMA/EL panels and some TFT panels.                                                                         |

| M<br>DE                 | 0          | 8maR         | 69                                                                                     | True<br>High         | This signal is used to provide the AC inversion<br>for flat panels to prevent a chemical damage. It<br>can also do as the display enable signal (DE)<br>for flat panel.                                             |

| P[23:16]<br>P[15:0]     | 0<br>0     | 4maR<br>8maR | 97,96,95,94,93,<br>92,91,90<br>88,87,86,85,84,<br>83,82,81,79,78,<br>76,75,74,73,72,71 | True                 | These signals contain RED/GREEN/BLUE color data for 9/12/18/24 bit interface TFT-color LCD panels.                                                                                                                  |

| SLD[7:0]                | 0          | 8maR         | 75,76,78,79,85,<br>86,87,88                                                            | True                 | These signals contain the lower data for color STN LCD panels.                                                                                                                                                      |

| SUD[7:0]                | 0          | 8maR         | 71,72,73,74,81,<br>82,83,84                                                            | True                 | These signals contain the upper data for color STN LCD panels .                                                                                                                                                     |

| LD[3:0]/ED[3:0]         | 0          | 8maR         | 75,76,78,79                                                                            | True<br>True         | These signals contain the lower data for gray dual-scan LCD panels .<br>These signals contain the even data for gray                                                                                                |

| UD[3:0]/OD[3:0]         | 0          | 8maR         | 71,72,73,74                                                                            | True<br>True         | PLASMA/EL panels .<br>These signals contain the upper data for gray<br>dual-scan LCD panels .<br>These signals contain the odd data for gray                                                                        |

| * Power Manag           | ement      | Pins (       | 5 pins)                                                                                | IIuc                 | PLASMA/EL panels .                                                                                                                                                                                                  |

| ACTI                    | I<br>(I/O) | -            | 53                                                                                     | High                 | The ACTI output is an active high signal that is<br>driven high every time a valid VGA access<br>(memory or I/O read/write).                                                                                        |

| FPVCC                   | 0          | 8maR         | 62                                                                                     | High                 | This signal is part of the flat panel power-down<br>sequencing and should be connected to the flat<br>panel LOGIC power enable . ( default = 0 after<br>reset-on)                                                   |

| FPVEE                   | 0          | 8maR         | 61                                                                                     | High                 | This signal is part of the flat panel power-down sequencing and should be connected to the flat panel BIAS power enable . (default = $0$ )                                                                          |

| FPBACK                  | 0          | 8maR         | 54                                                                                     | Low                  | This signal is part of the flat panel power-down sequencing and should be connected to the flat panel BACKLIGH enable . ( default = 1 )                                                                             |

| OFF                     | I/O        | 4maR         | 178                                                                                    | High                 | This input is used to force TP6508 into Off<br>mode enable . This pin can also redefined as an<br>output to indicate the active status . It may be<br>also configed as other function- by extended<br>register.     |

|               |          | Mono<br>LCD      | Color<br>LCD       | Color<br>LCD*    | Color<br>LCD     | Color<br>LCD | Color<br>LCD | Gray    | Gray  |

|---------------|----------|------------------|--------------------|------------------|------------------|--------------|--------------|---------|-------|

| Pin<br>Number | Pin Name | Dual-scan<br>STN | Single-scan<br>STN | Dual-scan<br>STN | Dual-scan<br>STN | TFT          | TFT          | PLASM   | EL    |

|               |          | 8-bit            | 16-bit             | 8-bit            | 16-bit           | 9/12/16-bit  | 18/24-bit    | 8-bit   | 8-bit |

| 70            | SHFCLK   | SCLK             | CL2                | CL2              | CL2              | DCLK         | DCLK         | CLK     | VCLK  |

| 68            | LP       | LCLK             | CL1                | CL1              | CL1              | LP/HS        | LP/HS        | HSYNC   | HS    |

| 67            | FLM      | FLM              | FLM                | FLM              | FLM              | FLM/VS       | FLM/VS       | VSYNC   | VS    |

| 69            | М        | MDL              | М                  | М                | М                | DE           | DE           | DISPTMG | DE    |

| 71            | P0       | UD3              | SUD7               | SUD7             | SUD7             | B0           | B0           |         |       |

| 72            | P1       | UD2              | SUD6               | SUD6             | SUD6             | B1           | B1           |         |       |

| 73            | P2       | UD1              | SUD5               | SUD5             | SUD5             | B2           | B2           |         |       |

| 74            | Р3       | UD0              | SUD4               | SUD4             | SUD4             | B3           | B3           |         |       |

| 75            | P4       | LD3              | SUD3               | SUD3             | SLD7             | B4           | B4           |         |       |

| 76            | Р5       | LD2              | SUD2               | SUD2             | SLD6             | G0           | B5           |         |       |

| 78            | P6       | LD1              | SUD1               | SUD1             | SLD5             | G1           | B6           |         |       |

| 79            | P7       | LD0              | SUD0               | SUD0             | SLD4             | G2           | B7           |         |       |

| 81            | P8       |                  | SLD7               |                  | SUD3             | G3           | G0           | OD3     | OD3   |

| 82            | Р9       |                  | SLD6               |                  | SUD2             | G4           | G1           | OD2     | OD2   |

| 83            | P10      |                  | SLD5               |                  | SUD1             | G5           | G2           | OD1     | OD1   |

| 84            | P11      |                  | SLD4               |                  | SUD0             | R0           | G3           | OD0     | OD0   |

| 85            | P12      |                  | SLD3               |                  | SLD3             | R1           | G4           | ED3     | ED3   |

| 86            | P13      |                  | SLD2               |                  | SLD2             | R2           | G5           | ED2     | ED2   |

| 87            | P14      |                  | SLD1               |                  | SLD1             | R3           | G6           | ED1     | ED1   |

| 88            | P15      |                  | SLD0               |                  | SLD0             | R4           | G7           | ED0     | ED0   |

| 90            | P16      |                  |                    |                  |                  |              | R0           |         |       |

| 91            | P17      |                  |                    |                  |                  |              | R1           |         |       |

| 92            | P18      |                  |                    |                  |                  |              | R2           |         |       |

| 93            | P19      |                  |                    |                  |                  |              | R3           |         |       |

| 94            | P20      |                  |                    |                  |                  |              | R4           |         |       |

| 95            | P21      |                  |                    |                  |                  |              | R5           |         |       |

| 96            | P22      |                  |                    |                  |                  |              | R6           |         |       |

| 97            | P23      |                  |                    |                  |                  |              | R7           |         |       |

# **Flat Panel Interface Table**

\* : Color Dual-scan STN LCD Panel with external frame buffer

| Symble       | Туре        | Drive | Pin Number                                                                  | Active | Function                                                                |

|--------------|-------------|-------|-----------------------------------------------------------------------------|--------|-------------------------------------------------------------------------|

| * Video Inte | rface (26 ] | pins) |                                                                             |        |                                                                         |

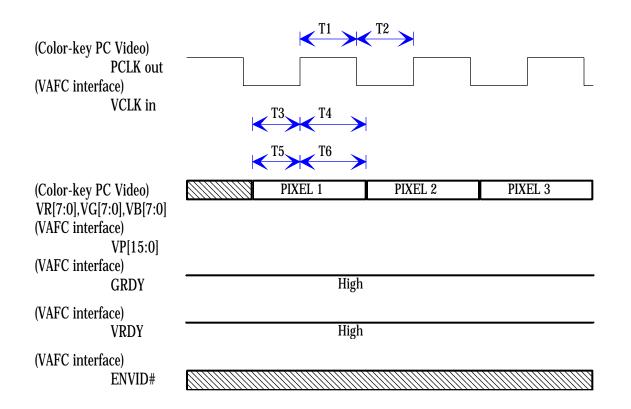

| VR[7:0]      | I/O         | 4maR  | 103,104,122,121,120,<br>119,100,154                                         | True   | Red data for the Video-In input by external PC Video system.            |

| VG[7:0]      | I/O         | 4maR  | 118,117,116,115,114,<br>113,98,99                                           | True   | Green data for the Video-In input by externa PC-Video system.           |

| VB[7:0]      | I/O         | 4maR  | 112,111,110,109,107,<br>106,54,53                                           | True   | Blue data for the Video-In input by external PC Video system.           |

| KEY          | I/O         | 4maR  | 101                                                                         | True   | Color key signal for the Video-In input by external PC-Video system.    |

| PCLK         | Ο           | 4maR  | 102                                                                         | True   | Pixel clock input of the Video-In interface b external PC-Video system. |

| VP[15:0]     | I/O         | 4maR  | 103,104,122,121,120,<br>118,117,116,115,114,<br>113,112,111,110,109,<br>107 | True   | VAFC interface video pixel data output.                                 |

| VRDY         | Ι           | -     | 101                                                                         | High   | VAFC interface video system ready signal.                               |

| GRDY         | О           | 4maR  | 119                                                                         | High   | VAFC interface graphics system ready signal.                            |

| EVID#        | Ι           | -     | 106                                                                         | Low    | VAFC interface enable video signal.                                     |

| VCLK         | Ι           | -     | 100                                                                         | True   | VAFC interface video input clock.                                       |

| * Power Pins | s (25 pins) |       |                                                                             |        |                                                                         |

| AVDD1        |             |       | 59                                                                          | +5V    | Internal DAC analog power.                                              |

| AVDD2        |             |       | 205                                                                         | +5V    | Internal MCLK frequency Synthesizer power.                              |

| AVDD3        |             |       | 206                                                                         | +5V    | Internal VCLK frequency Synthesizer power.                              |

| BVDD[1:2]    |             |       | 9,42                                                                        | +5V    | Host bus interface power.                                               |

| CVDD[1:2]    |             |       | 80,181                                                                      | +5V    | Core logical power.                                                     |

| DVDD         |             |       | 66                                                                          | +5V    | Digital pads output power.                                              |

| MVDDA        |             |       | 158                                                                         | +5V    | Memory bus A interface power.                                           |

| MVDDB        |             |       | 142                                                                         | +5V    | Memory bus B interface power.                                           |

| MVDDC        |             |       | 108                                                                         | +5V    | Memory bus C interface power.                                           |

| AVSS1        |             |       | 56                                                                          | Ground | Internal DAC analog ground.                                             |

| AVSS2        |             |       | 202                                                                         | Ground | Internal MCLK frequency Synthesizer analo                               |

|              |             |       |                                                                             | Ground | ground.                                                                 |

|           |             | <b>C</b> 1 | 1 5 5 6                                    |

|-----------|-------------|------------|--------------------------------------------|

|           |             | Ground     | ground.                                    |

| AVSS3     | 208         | Ground     | Internal VCLK frequency Synthesizer analog |

|           |             | Ground     | ground.                                    |

| BVSS[1:4] | 12,26,39,52 | Ground     | Host bus interface ground.                 |

| CVSS[1:2] | 77,184      | Ground     | Core logical ground.                       |

| DVSS[1:2] | 63,89       | Ground     | Digital pads output ground.                |

| MVSSA     | 161         | Ground     | Memory bus A interface ground.             |

| MVSSB     | 139         |            | Memory bus B interface ground.             |

| MVSSC     | 105         |            | Memory bus C interface ground.             |

|           |             |            |                                            |

### \*\*\* Descript of Type term

- O : Output I : Input

- I/O : Birdirectional

- OT : Output Tri-state

- I/S : Schmitt-trigger Input

- U : Internal passive pull-up

TOPRO

| Pin Type | Pin<br>Number | Pin Drive | ISA Bus  | PCI 32-Bit<br>Local Bus |

|----------|---------------|-----------|----------|-------------------------|

| I/O      | -             | 8maR      | SD[15:0] | AD[15:0]                |

| I/O      | 20            | 8maR      | OWS      | AD16                    |

| I/O      | 19            | 8maR      | MEMCS16* | AD17                    |

| I/O      | 18            | 8maR      | IOCS16*  | AD18                    |

| I/O      | -             | 8maR      |          | AD[31:19]               |

| Input    | 43            |           | SA0      | CBE0#                   |

| Input    | 32            |           | SBHE*    | CBE1#                   |

| Input    | 21            |           | S A 1    | CBE2#                   |

| Input    | 10            |           | REF*     | CBE3#                   |

| I/O      | -             | 4maR      | SA[19:2] | ROMA[17:0]              |

| Input    | -             |           | SA20     |                         |

| I/O      | -             | 4maR      | SA21     | ROMOE*                  |

| Input    | 201           |           | SA22     | CLK                     |

| Input    | 28            |           | SA23     |                         |

| I/O      | 29            | 8maR      | ROMCS*   | PERR#                   |

| I/O      | 30            | 8maR      | IRQ      | SERR#                   |

| I/O      | 53            | 8maR      | (ACTI)   | (ACTI)                  |

| I/O      | 54            | 8maR      | (FPBACK) | (FPBACK)                |

| Input    | 207           |           | RESET    | RST#                    |

| Input    | 22            |           | ALE      | FRAME#                  |

| I/O      | 31            | 4maR      | AEN      | PAR                     |

| Input    | 11            |           | MEMR*    | IDSEL                   |

| Input    | 23            |           | MEMW*    | IRDY#                   |

| ОТ       | 24            | 12maR     | IORDY*   | TRDY#                   |

| I/O      | 25            | 12maR     | IOWR*    | DEVSEL#                 |

| I/O      | 27            | 4maR      | IORD*    | STOP#                   |

# \* Host Bus Interface Table

[86.04.15

508BUS.TBL]

# \* Pin List

| Pin      | Pin    | Pin        | Pin          | Other Name(s) |

|----------|--------|------------|--------------|---------------|

| #        | Drive  | Туре       | Name         | (ISA Bus)     |

| 1        | 8maR   | I/O        | AD31         |               |

| 2        | 8maR   | I/O<br>I/O | AD31<br>AD30 |               |

| 3        | 8maR   | I/O        | AD30<br>AD29 |               |

| 4        | 8maR   | I/O        | AD29<br>AD28 |               |

| 5        | 8maR   | I/O        | AD23<br>AD27 |               |

| 6        | 8maR   | I/O<br>I/O | AD27<br>AD26 |               |

| 7        | 8maR   | I/O<br>I/O | AD25         |               |

| 8        | 8maR   | I/O<br>I/O | AD23<br>AD24 |               |

| 9        | olliak | Power      | BVDD1        |               |

| 10       |        | I          | CBE3#        | REF*          |

| 11       |        | I          | IDSEL        | MEMR*         |

| 11       |        | Ground     | BVSS1        | MEMK          |

| 12       | 8maR   | I/O        | AD23         |               |

| 13       | 8maR   | 1/O<br>1/O | AD23<br>AD22 |               |

| 14       |        | 1/0<br>1/0 | AD22<br>AD21 |               |

| 15       | 8maR   | 1/0<br>1/0 | AD21<br>AD20 |               |

| 10       | 8maR   | 1/0<br>1/0 |              |               |

|          | 8maR   |            | AD19         | LOCE1C*       |

| 18<br>19 | 8maR   | I/O        | AD18         | IOCS16*       |

| -        | 8maR   | I/O        | AD17         | MEMCS16*      |

| 20       | 8maR   | I/O        | AD16         | OWS           |

| 21       |        | I          | CBE2#        | SA1           |

| 22       |        | I          | FRAME#       | ALE           |

| 23       |        | I          | IRDY#        | MEMW*         |

| 24       | 12maR  | ОТ         | TRDY#        | IORDY*        |

| 25       | 12maR  | I/O        | DEVSEL       | IOWR*         |

| 26       |        | Ground     | BVSS2        |               |

| 27       | 12maR  | I/O        | STOP         | IORD*         |

| 28       |        | I          |              | LA23          |

| 29       | 8maR   | I/O        | PERR#        | ROMCS*        |

| 30       | 8maR   | I/O        | SERR#        | IRQ           |

| 31       | 4maR   | I/O        | PAR          | AEN           |

| 32       |        | I          | CBE1#        | SBHE*         |

| 33       | 8maR   | I/O        | AD15         | SD15          |

| 34       | 8maR   | I/O        | AD14         | SD14          |

| 35       | 8maR   | I/O        | AD13         | SD13          |

| 36       | 8maR   | I/O        | AD12         | SD1           |

| 37       | 8maR   | I/O        | AD11         | SD11          |

| 38       | 8maR   | I/O        | AD10         | SD10          |

| 39       |        | Ground     | BVSS3        |               |

| 40       | 8maR   | I/O        | AD9          | SD9           |

| 41       | 8maR   | I/O        | AD8          | SD8           |

| 42       |        | Power      | BVDD2        |               |

| 43       |        | I          | CBE0#        | SA0           |

| 44       | 8maR   | I/O        | AD7          | SD7           |

| 45       | 8maR   | I/O        | AD6          | SD6           |

| 46       | 8maR   | I/O        | AD5          | SD5           |

| 47       | 8maR   | I/O        | AD4          | SD4           |

| 48       | 8maR   | I/O        | AD3          | SD3           |

| 49       | 8maR   | I/O        | AD2          | SD2           |

| 50       | 8maR   | I/O        | AD1          | SD1           |

| 51       | 8maR   | I/O        | AD0          | SD0           |

| 52       |        | Ground     | BVSS4        |               |

| Pin      | Pin          | Pin              | Pin        | 1                 |

|----------|--------------|------------------|------------|-------------------|

| #        | Drive        | Туре             | Name       | Other Name(s)     |

| 53       | 8maR         | I/O              | ACTI       | VB0,SDA,CSYNC     |

| 54       | 8maR         | I/O              | FPBACK     | VB1,SCL,CSYNC     |

| 55       | 10ma         | Analog<br>Output | RSET       |                   |

| 56       |              | Ground           | AVSS1      |                   |

| 57       | 20ma         | Analog           | BLUE       |                   |

| 58       | 20ma         | Output<br>Analog | GREEN      |                   |

| 59       | 20111        | Output<br>Power  | AVDD1      |                   |

| 60       | 20ma         | Analog           | RED        |                   |

| 61       | 20ma         | Output<br>O      | FPVEE      | FPBACK            |

| 62       | 20ma         | 0                | FPVCC      | TIDACK            |

| 63       | Zoma         | Ground           | DVSS1      |                   |

| 64       | 12maR        | 0                | VSYNC      |                   |

| 65       | 12maR        | 0                | HSYNC      | CSYNC             |

| 66       |              | Power            | DVDD       |                   |

| 67       | 8maR         | ОТ               | FLM        |                   |

| 68       | 8maR         | ОТ               | LP         |                   |

| 69       | 8maR         | 0                | Μ          |                   |

| 70       | 12maR        | 0                | SHFCLK     |                   |

| 71       | 8maR         | 0                | P0         |                   |

| 72       | 8maR         | 0                | P1         |                   |

| 73       | 8maR         | 0                | P2         |                   |

| 74       | 8maR         | 0                | P3         |                   |

| 75       | 8maR         | 0                | P4         |                   |

| 76       | 8maR         | 0                | P5         |                   |

| 77       | 0 <b>D</b>   | Ground           | CVSS1      |                   |

| 78<br>79 | 8maR<br>8maR | 0                | P6<br>P7   |                   |

| 80       | olliak       | Power            | CVDD1      |                   |

| 81       | 8maR         | 0                | P8         |                   |

| 82       | 8maR         | 0                | P9         |                   |

| 83       | 8maR         | 0                | P10        |                   |

| 84       | 8maR         | 0                | P11        |                   |

| 85       | 8maR         | 0                | P12        |                   |

| 86       | 8maR         | 0                | P13        |                   |

| 87       | 8maR         | 0                | P14        |                   |

| 88       | 8maR         | 0                | P15        |                   |

| 89       |              | Ground           | DVSS2      |                   |

| 90       | 4maR         | 0                | P16        | CA0               |

| 91       | 4maR         | 0                | P17        | CA1               |

| 92       | 4maR         | 0                | P18        | CA2               |

| 93       | 4maR         | 0                | P19        | CA3               |

| 94<br>95 | 4maR         | 0                | P20        | CA4               |

|          | 4maR         | 0                | P21        | CA5               |

| 96<br>97 | 4maR         | 0                | P22<br>P23 | CA6<br>CA7        |

| 97<br>98 | 4maR<br>4maR | I/O              | P23<br>VG1 | CA8               |

| 90<br>99 | 4maR         | I/O<br>I/O       | VGI        | CA9               |

| 100      | 4maR         | I/O<br>I/O       | VGU<br>VR1 | VCLK,OEC*         |

| 100      | 4maR         | I/O<br>I/O       | KEY        | VRDY,RASC*        |

| 101      | 4maR         | 0                | PCLK       | WEC*,WECH*        |

| 102      | 4maR         | I/O              | VR7        | VP15,CASCL*,WECL* |

| 104      | 4maR         | I/O              | VR6        | VP15,CASCH*,CASC* |

|          |              |                  |            | P23               |

| Pin        | Pin          | Pin            | Pin            | Other Name(s) |

|------------|--------------|----------------|----------------|---------------|

| #          | Drive        | Туре           | Name           |               |

| 105        |              | Ground         | MVSSC          |               |

| 106        | 4maR         | I/O            | VB2            | EVID#,MCD0    |

| 107        | 4maR         | I/O            | VB3            | VP0,MCD1      |

| 108        |              | Power          | MVDDC          |               |

| 109        | 4maR         | I/O            | VB4            | VP1,MCD2      |

| 110        | 4maR         | I/O            | VB5            | VP2,MCD3      |

| 111        | 4maR         | I/O            | VB6            | VP3,MCD4      |

| 112        | 4maR         | I/O            | VB7            | VP4,MCD5      |

| 113        | 4maR         | I/O            | VG2            | VP5,MCD6      |

| 114        | 4maR         | I/O            | VG3            | VP6,MCD7      |

| 115        | 4maR         | I/O            | VG4            | VP7,MCD8      |

| 116        | 4maR         | I/O            | VG5            | VP8,MCD9      |

| 117        | 4maR         | I/O            | VG6            | VP9,MCD10     |

| 118        | 4maR         | I/O            | VG7            | VP10,MCD11    |

| 119        | 4maR         | I/O            | VR2            | GRDY,MCD12    |

| 120        | 4maR         | I/O            | VR3            | VP11,MCD13    |

| 121        | 4maR         | I/O            | VR4            | VP12,MCD14    |

| 122        | 4maR         | I/O            | VR5            | VP13,MCD15    |

| 123        | 4maR         | 0              | RASB*          |               |

| 124        | 4maR         | 0              | WEB*           | WEBH*,AA9     |

| 125        | 4maR         | 0              | CASBH          | CASB*         |

| 126        | 4maR         | 0              | CASBL*         | WEBL*         |

| 127        | 4maR         | I/O            | MBD0           |               |

| 128        | 4maR         | I/O            | MBD1           |               |

| 129        | 4maR         | I/O            | MBD2           |               |

| 130        | 4maR         | I/O            | MBD3           |               |

| 131        | 4maR         | I/O            | MBD4           |               |

| 132        | 4maR         | I/O            | MBD5           |               |

| 133        | 4maR         | I/O            | MBD6           |               |

| 134        | 4maR         | I/O            | MBD7           |               |

| 135        | 4maR         | I/O            | MBD8           |               |

| 136        | 4maR         | I/O            | MBD9           |               |

| 137        | 4maR         | I/O<br>I/O     | MBD10          |               |

| 138        | 4maR         |                | MBD11<br>MVCCD |               |

| 139        | 4m c D       | Ground<br>I/O  | MVSSB<br>MBD12 |               |

| 140<br>141 | 4maR<br>4maR | I/O<br>I/O     | MBD12<br>MBD13 |               |

| 141        | 41114K       | Power          | MVDDB          |               |

| 143        | 4maR         | I/O            | MBD14          |               |

| 143        | 4maR         | I/O<br>I/O     | MBD14<br>MBD15 |               |

| 144        | 4maR         | I/O/U          | AA0            | CFG0          |

| 145        | 4maR         | I/O/U<br>I/O/U | AAU<br>AA1     | CFG1          |

| 147        | 4maR         | I/O/U          | AA1<br>AA2     | CFG2          |

| 148        | 4maR         | I/O/U          | AA2<br>AA3     | CFG3          |

| 149        | 4maR         | I/O/U          | AA4            | CFG4          |

| 150        | 4maR         | I/O/U          | AA5            | CFG5          |

| 150        | 4maR         | I/O/U          | AA6            | CFG6          |

| 151        | 4maR         | I/O/U          | AA7            | CFG7          |

| 153        | 4maR         | I/O/U          | AA8            | CFG8          |

| 153        | 4maR         | I/O            | VR0            | 32KHZ         |

| 155        | 8maR         | 0              | OEAB*          |               |

| 156        | 4maR         | 0              | RASA*          |               |

| 150        | THIAN        | Ÿ              | NADA           |               |

| Pin | Pin   | Pin    | Pin    |               |

|-----|-------|--------|--------|---------------|

| #   | Drive | Туре   | Name   | Other Name(s) |

| 157 | 4maR  | 0      | WEA*   | WEAH*         |

| 158 |       | Power  | MVDDA  |               |

| 159 | 4maR  | 0      | CASAH* | CASA*         |

| 160 | 4maR  | 0      | CASAL* | WEAL*         |

| 161 |       | Ground | MVSSA  |               |

| 162 | 4maR  | I/O/U  | MAD0   |               |

| 163 | 4maR  | I/O/U  | MAD1   |               |

| 164 | 4maR  | I/O/U  | MAD2   |               |

| 165 | 4maR  | I/O/U  | MAD3   |               |

| 166 | 4maR  | I/O/U  | MAD4   |               |

| 167 | 4maR  | I/O/U  | MAD5   |               |

| 168 | 4maR  | I/O/U  | MAD6   |               |

| 169 | 4maR  | I/O/U  | MAD7   |               |

| 170 | 4maR  | I/O/U  | MAD8   |               |

| 171 | 4maR  | I/O/U  | MAD9   |               |

| 172 | 4maR  | I/O/U  | MAD10  |               |

| 173 | 4maR  | I/O/U  | MAD11  |               |

| 174 | 4maR  | I/O/U  | MAD12  |               |

| 175 | 4maR  | I/O/U  | MAD13  |               |

| 176 | 4maR  | I/O/U  | MAD14  |               |

| 177 | 4maR  | I/O/U  | MAD15  |               |

| 178 | 4maR  | I/O    | OFF    | EXVCLK        |

| 179 | 4maR  | I/O    | ROMA0  | SA2           |

| 180 | 4maR  | I/O    | ROMA1  | SA3           |

| 181 |       | Power  | CVDD2  |               |

| 182 | 4maR  | I/O    | ROMA2  | SA4           |

| 183 | 4maR  | I/O    | ROMA3  | ,SA5          |

| 184 |       | Ground | CVSS2  |               |

| 185 | 4maR  | I/O    | ROMA4  | SA6           |

| 186 | 4maR  | I/O    | ROMA10 | SA7           |

| 187 | 4maR  | I/O    | ROMA5  | SA8           |

| 188 | 4maR  | I/O    | ROMA11 | SA9           |

| 189 | 4maR  | I/O    | ROMA6  | SA10          |

| 190 | 4maR  | I/O    | ROMA9  | SA11          |

| 191 | 4maR  | I/O    | ROMA7  | SA12          |

| 192 | 4maR  | I/O    | ROMA8  | SA13          |

| 193 | 4maR  | I/O    | ROMA12 | SA14          |

| 194 | 4maR  | I/O    | ROMA13 | SA15          |

| 195 | 4maR  | I/O    | ROMA14 | SA16          |

| 196 | 4maR  | I/O    | ROMA15 | LA17          |

| 197 | 4maR  | I/O    | ROMA16 | LA18          |

| 198 | 4maR  | I/O    | ROMA17 | LA19          |

| 199 |       | I      |        | LA20          |

| 200 | 4maR  | I/O    | ROMOE  | LA21          |

| 201 |       | I      | CLK    | LA22          |

| 202 |       | Ground | AVSS2  |               |